One major trend in the field of computing has been the customization of hardware has gained popularity along with the rise of heterogeneous computing and hardware acceleration. Out of this trend came the RISC-V architecture, an open-source ISA that has enabled thousands of cheap and accessible custom hardware designs.

One company that has been championing the RISC-V movement has been Microchip, which has been developing RISC-V-based hardware since at least 2019.

Recently, Microchip has continued this trend as it announced that its RISC-V-based PolarFire SoC FPGA had reached mass production. Along with this, Microchip has also announced continual support for their Mi-V ecosystem, helping drive RISC-V adoption.

A high-level overview of Microchip's Mi-V ecosystem. Image used courtesy of Microchip

In this article, we’ll look at the reasons for pairing RISC-V and FPGAs, the PolarFire SoC FPGA, and the Mi-V Ecosystem.

Blending FPGAs and RISC-V

One of Microchip’s crowning achievements in the RISC-V world has been its PolarFire SoC, a piece of hardware that builds a RISC-V system out of FPGA fabric. Naturally, this raises the question: why blend FPGAs and RISC-V together?

An answer to this question is that RISC-V and FPGAs are both designed to do a similar thing—provide users with flexibility and customization. FPGAs are software-defined hardware, meaning users can write specialized hardware description language (HDL) code to shape their FPGA fabric into custom computing blocks and hardware accelerators.

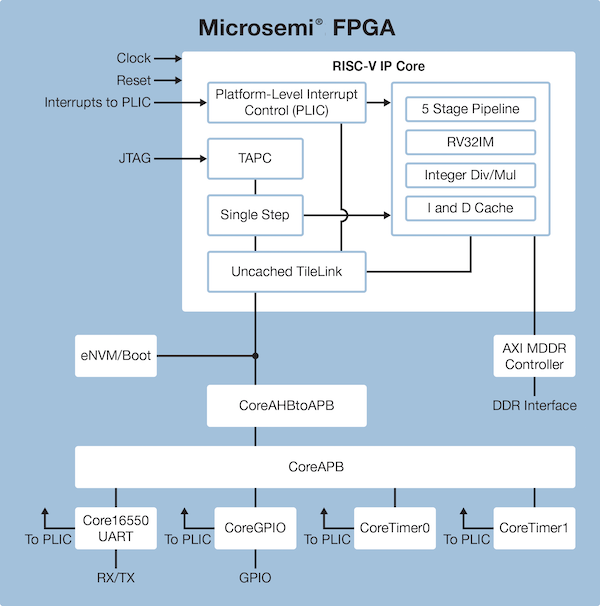

An example block diagram with a blend of RISC-V and FPGA. Image used courtesy of Microchip

By the same token, RISC-V was developed to make hardware design and customization accessible to everyone.

In this way, the merger between FPGAs and RISC-V can make perfect sense. The combination affords designers a highly customizable, open-source platform to rapidly iterate, customize, and optimize their designs for their intended use cases.

PolarFire SoC FPGA

Microchip made headlines in the RISC-V world this week when it announced that its PolarFire SoC FPGA had entered mass production.

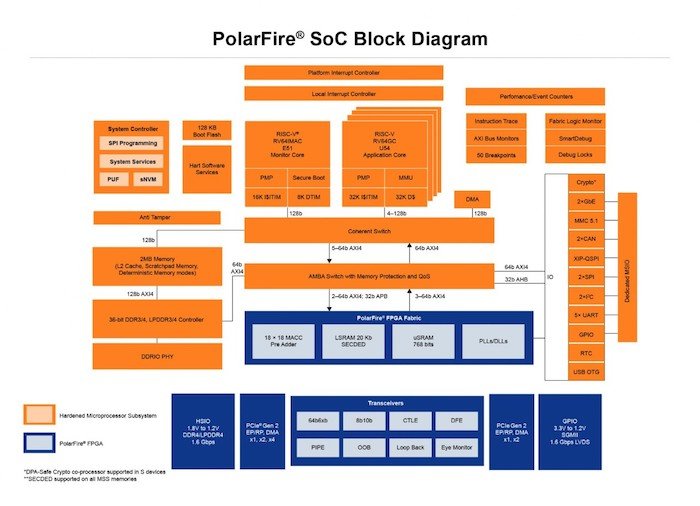

As AAC contributor Lisa Boneta previously described, Microchip’s PolarFire SoC is a RISC-V-based SoC built entirely on FPGA fabric. The system consists of a RISC-V microprocessor subsystem in hardened FPGA logic, coupled with the PolarFire FPGA portion of the SoC. The highlights of the hardened microprocessor subsystem consist of a system controller, a RISC-V monitor core, a quad-core RISC-V application cluster, and a deterministic L2 memory subsystem. On the FPGA side, the SoC features up to 460K logic elements, 12.7 Gbps transceivers, and PCIe 2 I/O.

PolarFire SoC block diagram. Image used courtesy of Microchip [click to enlarge]

Altogether Microchip lauds the PolarFire SoC, claiming it delivers up to 50% lower power than comparable FPGAs. The company quantifies this, by stating that at 1.3 W, the PolarFire SoC can deliver up to 6500 CoreMarks as opposed and consumes 55% lower power at 8000 CoreMarks than competitors.

Mi-V Ecosystem

Along with the mass production of the PolarFire SoC, Microchip has also announced continual support of its Mi-V Ecosystem.

Mi-V is a RISC-V ecosystem that provides users with a comprehensive set of tools and resources to support RISC-V designs. These tools include a variety of:

- IP

- Hardware

- Operating systems

- Middleware

- Debuggers

- Compilers

- Design services

Within this, the ecosystem includes software RISC-V CPUs targeted for FPGA fabric and the hard CPU cores seen in the PolarFire SoC.

Overall, the goal of the Mi-V ecosystem is to drive the adoption of the RISC-V architecture by providing designers with tools and resources that remove the barriers to entry for RISC-V design.

RISC-V Industry Impacts

All things considered, this announcement from a Microchip is a big deal as it marks the industry’s first RISC-V-Based SoC FPGA to enter volume production.

On a smaller scale, it means that more designers and engineers will be exposed to RISC-V and have the ability to design custom hardware easily. On a larger scale, this is indicative of the industry’s acceptance of RISC-V and the future it has the potential to play in the industry at large.