The RISC-V open instruction set architecture is a popular alternative to proprietary architectures available today, such as those by ARM. Since its birth, RISC-V has steadily gained academic and commercial popularity.

Understanding RISC vs CISC

RISC is a computer architecture philosophy proposed in the 1980s as an alternative to the commercial architectures offered at the time by Intel, Motorola, and pretty much everyone else. Originally dubbed as "Complex Instruction Set Computer," or CISC, this architecture relied on dense instruction sets to implement a wide variety of operations thought to be useful and necessary. However, many research teams including IBM and UC Berkeley found that compilers usually ended up using a very small subset of these complex instruction sets. This, and other findings, led to questioning the need for a larger instruction set, focusing on simplicity as a means to improve efficiency.

Overall, RISC is the opposite of CISC in many ways. Usually, CISC central processing units (CPUs) have a few registers and lots of instructions, most of which have access to memory, whereas RISC CPUs have lots of registers and a very modest instruction set, with memory access restricted to a few load and store instructions.

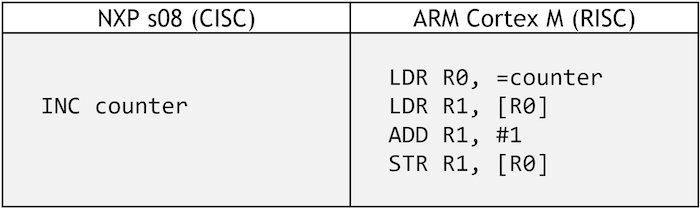

To illustrate the difference between complex and simple instructions, Table 1 shows a code comparison between incrementing a counter variable with a CISC CPU (the s08 by NXP), and a RISC CPU (the ARM Cortex M0+).

Table 1. An example comparison between CISC and RISC codes.

In this table, CISC allows incrementing a variable in a single instruction, while RISC needs to access memory with load and store. Although this shows a difference in code size, it is not an apples-to-apples comparison because there are many differences between the architectures, so this does not prove that one is technically better than the other.

Today, the Intel x86/x64 architecture is proof that CISC microprocessors were not replaced by RISC, and the ARM architecture is proof that RISC has dominated the mobile device market.

RISC-V History

The RISC acronym was coined around 1980 by Prof. David Patterson at the University of California, Berkeley, whose work with Prof. John Hennessy at Stanford University yielded their celebrated books “Computer Organization and Design” and “Computer Architecture: A Quantitative Approach." Thanks to their work on the RISC architecture, they received the ACM A.M. Turing Award in 2017.

Fast forward from 1980 to 2010, the development of the fifth generation of the RISC research project started, and eventually came to be known as RISC-V (pronounced "risk-five").

RISC-V International—An Open ISA

RISC-V is an open instruction set architecture (ISA), which means that you are free to implement a RISC-V CPU in a microprocessor or microcontroller without having to pay royalties to anyone for using this ISA.

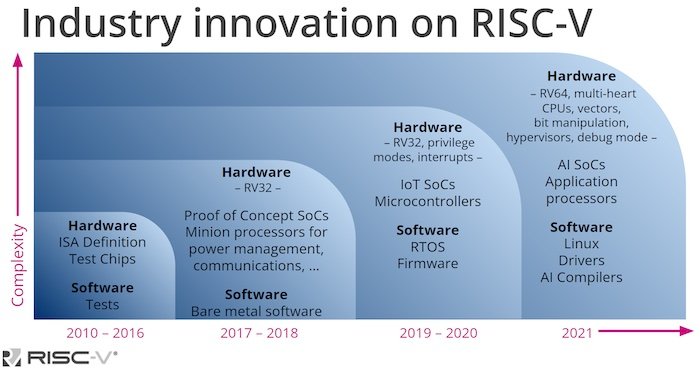

RISC-V International is a global nonprofit organization that owns and maintains the RISC-V ISA intellectual property. One of its main goals is to keep the design of RISC-V based on simplicity and performance, as opposed to focusing on commercial interests. For this reason, RISC-V International relies on its members, who represent the microprocessor ecosystem population, ranging from individuals to organizations like Google, Intel, and Nvidia. Becoming a member has a host of benefits, including the possibility of contributing to the design of the ISA, and voting to approve proposed changes. Below in Figure 1, you can see a high-level timeline of the development of RISC-V over the years.

Figure 1. Since its inception in 2010, RISC-V has been well received by the microprocessor industry, and adoption has been steadily growing both in hardware and software. Image used courtesy of RISC-V International

Conventions for a RISC-V ISA and Extensions

Being the fifth generation of a research project that started in 1980, RISC-V is a seasoned architecture designed to succeed where others might have failed in the past, RISC-V aims to learn from any potential past mistakes.

For this reason, RISC-V was designed as a modular ISA, as opposed to the traditional incremental ISAs. This means that a RISC-V implementation is composed of a mandatory base ISA and a number of ISA extensions, so that custom CPUs may be tailored to the application’s needs.

The naming convention for custom ISAs consists of the letters RV (for RISC-V) followed by the bit width and an identifier for the variant.

For example, RV32IMAC, shown in Figure 2, means:

- RV32I: A 32-bit CPU with the Base Integer ISA

- M: The Integer Multiplication and Division extension

- A: The Atomic Instruction extension

- C: The Compressed Instruction extension

Figure 2. The instruction set for the RV32IMAC ISA shows the modular (not incremental) nature of RISC-V. A mandatory Base ISA is combined with a set of extensions [click to enlarge].

Compilers are informed of the extensions included in the target CPU so that it generates the best possible code. If the code has instructions from missing extensions, the hardware traps and executes software functions from the standard library.

Base Integer ISA

With only 47 instructions, the RV32I base integer ISA implements the absolutely necessary operations to achieve basic functionality with 32-bit integers (its 64-bit variant is RV64I). This ISA, encoded in 32-bits, includes instructions for:

- Addition

- Subtraction

- Bitwise operations

- Load and store

- Jumps

- Branches

The base ISA also specifies the 32 CPU registers, which are all 32-bits wide, plus the program counter. The only special register is x0, which always reads 0, as implemented in many previous RISC ISAs.

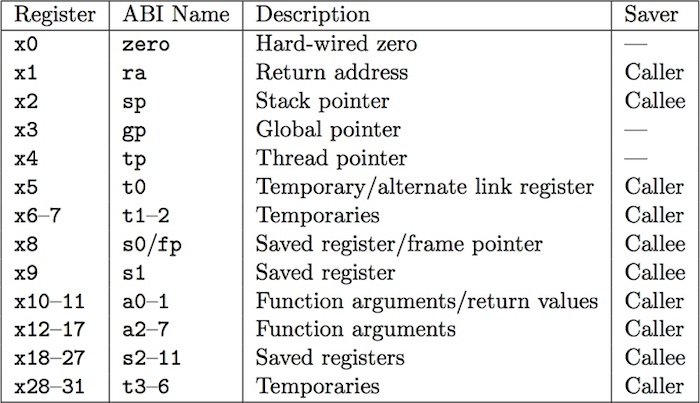

Although all registers, some shown in Table 2, are available for general purposes, the application binary interface (ABI) specifies a purpose for each of them, according to its calling convention. This means that some registers are supposed to hold temporary or saved data, pointers, return addresses, and so on.

Table 2. The RV32I register file shows the hardware register names and their assigned functionality as specified in the RISC-V application binary interface. Image used courtesy of Krste Asanović and Randy H. Katz

RISC-V Multiplication and Floating Point

The RV32M extension implements 8 instructions to perform multiplications and divisions on integers (RV64M adds 5 instructions to those 8).

The RV32F extension adds 32 separate registers for 32-bit floating-point numbers and 26 floating-point instructions. Similarly, the RV32D extension uses 32 64-bit floating-point registers, with support for double-precision 64-bit floating-point numbers.

RISC-V Compressed Instructions

The RV32C extension is a clever addition to the RISC-V ISA because it provides an alternative 16-bit encoding for a special subset of existing instructions.

After analyzing countless lines of code generated by modern optimizing compilers, the creators of RISC-V identified the most popular instructions, and created 16-bit versions, giving up some of the functionality of their full 32-bit versions, which are still available in the RV32I base ISA anyway.

This compression is possible because of these instructions:

- Some registers are more popular than others.

- One operand is usually overwritten.

- There are some preferred immediate values.

This allows encoding the instructions for a limited number of registers as operands, specifying only 2 registers instead of 3, using small immediate values, all of this in 16 bits.

By compressing the most frequently used instructions, you have a better chance of compressing your programs significantly.

Other RISC-V Extensions

There’s a host of additional extensions, which implement every functionality you may expect from a modern microprocessor. This includes an Embedded Base ISA (RV32E), extensions for Atomic Operations (A), Bit Manipulation (B), Vector Operations (V), and the list goes on.

RISC-V Implementation

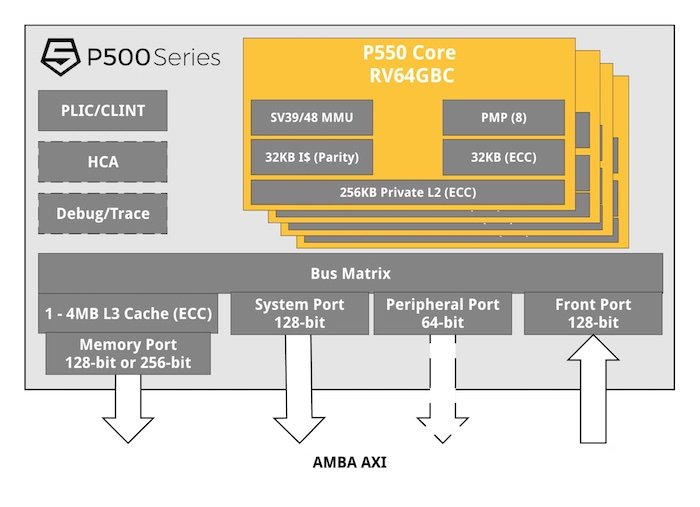

There are a number of companies manufacturing all variants of RISC-V cores in their microcontrollers, microprocessors, and SoCs. One example is SiFive, the first company to manufacture silicon-based on the RISC-V ISA. Their chips range from low-end microcontrollers all the way to high-performance SoCs.

Figure 3. An example of a RISC-V block diagram, namely that of the P550 high-performance application processor. Image used courtesy of SiFive

However, practical RISC-V projects are not restricted to integrated circuits. There’s an impressive number of ongoing projects in many areas like compilers, simulators, development environments, operating systems, and so on. For a detailed list of projects, you can visit this GitHub to learn more.

All in all, RISC-V is an exciting topic in the world of computer architecture, and today is a great time to join in on the fun. If you’d like to learn more about this movement, be sure to visit the RISC-V International website.

![The instruction set for the RV32IMAC ISA shows the modular (not incremental) nature of RISC-V. A mandatory Base ISA is combined with a set of extensions [click to enlarge].](/files/article/jpg/20220911/138821797862232640.jpg)