Synopsys has reported that NSITEXE has successfully produced the first prototype, or “first silicon”, of its Data Flow Processor (DFP). This milestone was achieved through the use of Synopsys’s design, verification, and IP solutions.

The specialized architecture of NSITEXE’s DFP combines a CPU and a GPU. It is targeted at processing large and complex datasets and allows for parallel data management—important criteria for success in autonomous driving applications.

According to Yukihide Niimi, President and CEO at NSITEXE, the company's IP (intellectual property) solutions "enable various applications such as next-generation automotive systems with autonomous drive, robotics, factory automation, and IoT.

NSITEXE was established in 2017 by DENSO, a Japan-based global manufacturer of automotive parts. NSITEXE’s purpose was defined with a focus on designing components that enable automated driving, including semiconductor IP cores. The pathway for the DFC chip was originally charted by the parent company.

Synopsys’ design, test, and verification solutions—as well as its DesignWare IP—were central to NSITEXE's success with its new DFP chip.

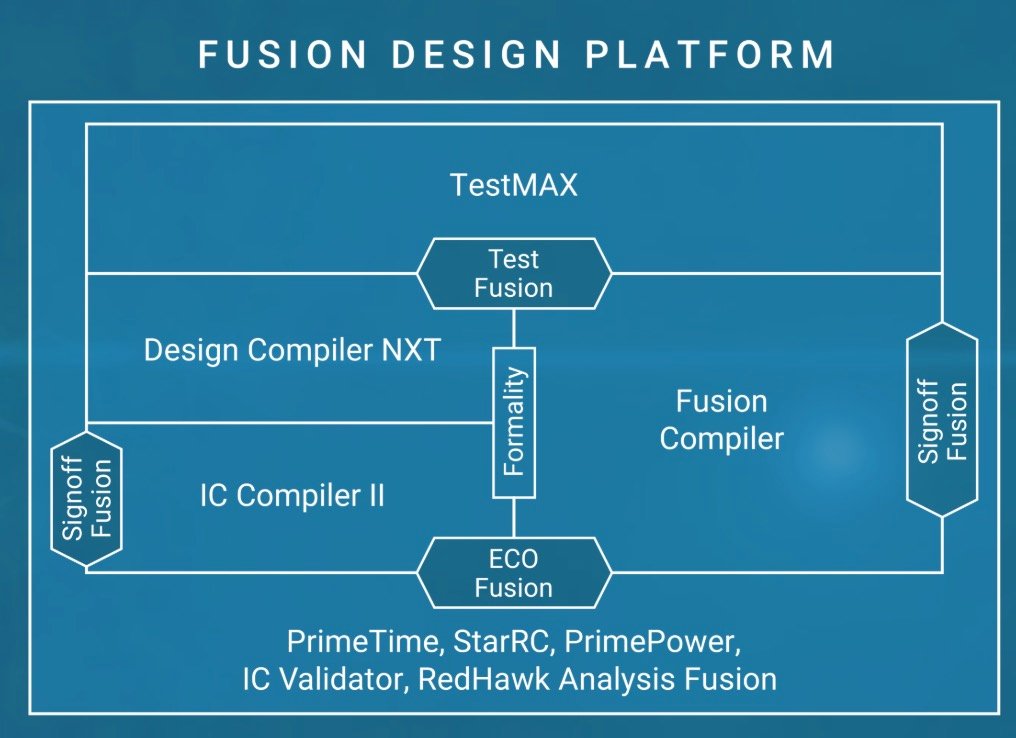

The Fusion Design Platform

The Fusion Design Platform is an AI-enhanced platform that merges the company’s synthesis, place and route, and DFT (design for test) by sharing engines. Under Fusion technology, place and route and synthesis routinely call on each other to enable faster and better convergence. Fusion is available on Amazon Web services, Microsoft Azure, and the Synopsys Cloud Solution.

The Fusion Design Platform. Image from Synopsys

Synopsys’ Design Tools enable engineers to develop advanced digital, custom, and analog/mixed-signal designs. The company claims that most of today’s FinFET (multi-gate MOSFET) designs have been implemented with Synopsys tools. Additionally, Synopsys and Arm are collaborating to implement Arm's newest client and infrastructure cores

Synopsys’ TestMAX family of products offer test and diagnosis capabilities for all digital, memory and analog portions of a semiconductor device. Early validation of complex DFT logic is supported via full RTL (register-transfer level) integration. Direct links into the Synopsys Fusion Design Platform maintain physical, timing and power awareness.

Synopsys’ Verification Tools enables designers to find SoC bugs earlier in the design cycle and more easily validate the entire hardware and software system.

Synopsys’ DesignWare IP

Synopsys’ DesignWare portfolio of IP solutions for SoC designs includes logic libraries, embedded memories, analog IP, wired and wireless interface IP, security IP, embedded processors, and subsystems. The company provides an online catalog of available IP, which is extensive.

As described by Kimio Fujii, President of Synopsys Japan, "Our integrated EDA, silicon-proven IP, and software security and quality solutions are widely used by industry-leading companies in automotive, AI, networking, and mobile applications." He goes on to state that, "The successful development of NSITEXE's advanced SoC test chip demonstrates how our solutions accelerate time-to-market of the next-generation processors."

Synopsys will be describing its successful work with NSITEXE at the Synopsys User Group (SNUG) Japan. The group will meet on September 13, 2019 at the PAMIR International Convention Center in Shinagawa, Tokyo.

In July, Cadence announced that they, too, were partnering with NSITEXE, boasting that NSITEXE was able to accomplish a "reduced turnaround time by 75%" by utilizing Cadence's digital design flow, Genus Synthesis Solution.

If you'd like to learn more, check out my roundup where I compare and contrast some EDA software programs for IC design, including Synopsys, Cadence, Mentor, and AIDAsoft.

How often do you rely on EDA tools like these for your design work? Tell us about it in the comments below.