White Paper Overview

EDA suppliers constantly evaluate design information from both design houses and foundries to assess the impact of changing technology and to develop and implement new functionality and tools that reduce time and resource impacts while improving accuracy and full coverage.

As the semiconductor industry strives to keep Moore’s Law moving forward, companies are continually confronted with new and mounting challenges. The use of fin field-effect transistors (finFETs) and the recent introduction of gate-all-around (GAA) finFETs present questions of performance, scalability, and variation resilience that have yet to be fully resolved. The need for multi-patterning, which has been in place since the 22 nm node, is not going away, even with the introduction of extreme ultraviolet (EUV) lithography. Complex fill requirements have emerged as a critical success factor in both manufacturability and performance in leading-edge nodes.

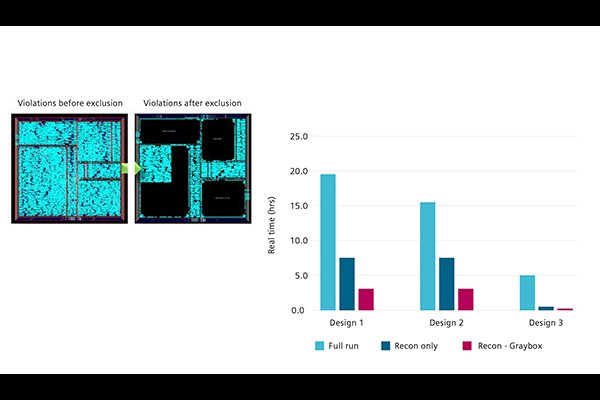

This white paper takes a look at replacing inefficient, less precise verification processes with smarter, more accurate, faster, and efficient functionality that can improve both the bottom line and product quality, even in increasing technological complexity.